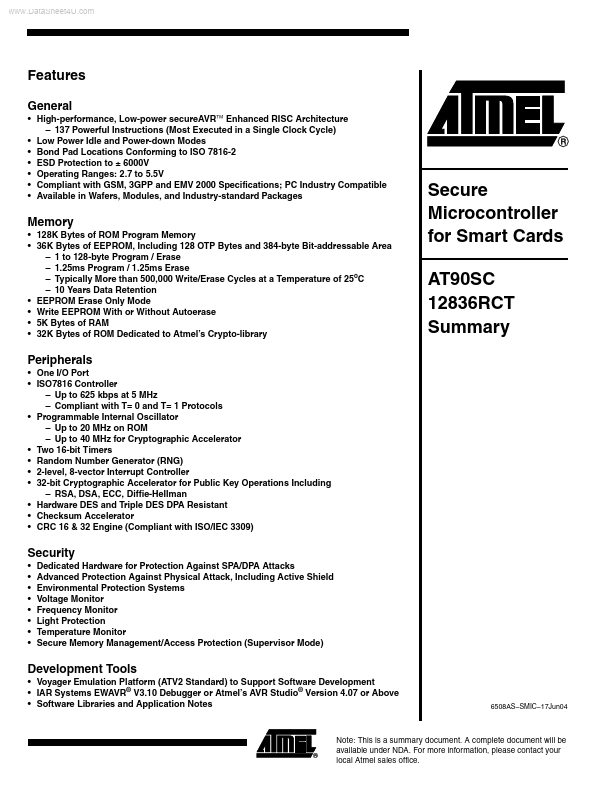

AT90SC12836RCT

AT90SC12836RCT is Secure Microcontroller manufactured by Atmel.

Features

General

- High-performance, Low-power secure AVR™ Enhanced RISC Architecture

- -

- -

- -

- 137 Powerful Instructions (Most Executed in a Single Clock Cycle) Low Power Idle and Power-down Modes Bond Pad Locations Conforming to ISO 7816-2 ESD Protection to ± 6000V Operating Ranges: 2.7 to 5.5V pliant with GSM, 3GPP and EMV 2000 Specifications; PC Industry patible Available in Wafers, Modules, and Industry-standard Packages

Memory

- 128K Bytes of ROM Program Memory

- 36K Bytes of EEPROM, Including 128 OTP Bytes and 384-byte Bit-addressable Area

- 1 to 128-byte Program / Erase

- 1.25ms Program / 1.25ms Erase

- Typically More than 500,000 Write/Erase Cycles at a Temperature of 25o C

- 10 Years Data Retention EEPROM Erase Only Mode Write EEPROM With or Without Autoerase 5K Bytes of RAM 32K Bytes of ROM Dedicated to Atmel’s Crypto-library

Secure Microcontroller for Smart Cards AT90SC 12836RCT Summary

- -

- -

Peripherals

- One I/O Port

- ISO7816 Controller

- -

- -

- -

- -

- Up to 625 kbps at 5 MHz

- pliant with T= 0 and T= 1 Protocols Programmable Internal Oscillator

- Up to 20 MHz on ROM

- Up to 40 MHz for Cryptographic Accelerator Two 16-bit Timers Random Number Generator (RNG) 2-level, 8-vector Interrupt Controller 32-bit Cryptographic Accelerator for Public Key Operations Including

- RSA, DSA, ECC, Diffie-Hellman Hardware DES and Triple DES DPA Resistant Checksum Accelerator CRC 16 & 32 Engine (pliant with ISO/IEC...